# EMBEDDED SYSTEMS VOLUME 5 NUMBER 8 NOV/DEC 2009

INCLUDING

#### Chris A. Ciufo

C4ISR and the big picture

#### Field Intelligence

Packet processors; mil networks

#### Mil Tech Insider

High-voltage boosts modernization

#### Legacy Software Migration

Micro Focus

COBOL gets modern

Targeting secure and reliable systems

Also:

Mobile power for tomorrow's battlefield

**Static analysis: Beyond the compiler**

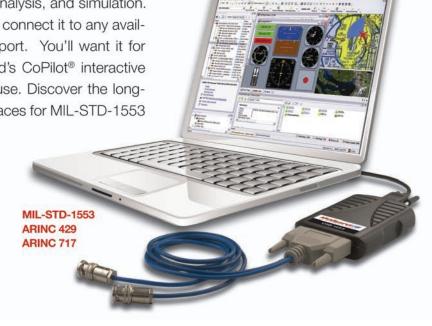

# Put a new tool in your pocket.

#### **USB-Powered Avionics Databus Interfaces**

One small tool does it all – databus test, analysis, and simulation. Use it around the lab or in the field. Simply connect it to any available PC – it's fully powered by the USB port. You'll want it for all your interface applications. Add Ballard's CoPilot® interactive software for extra versatility and ease-of-use. Discover the long-lasting benefits of Ballard's new USB interfaces for MIL-STD-1553 and ARINC 429 and 717.

Call us today at 425.339.0281.

The Avionics Databus Innovators

AS9100 / ISO 9001 Registered

www.ballardtech.com

Vicor Custom Power: Small company responsiveness, large company resources

The sole focus of Vicor Custom Power is designing and manufacturing turnkey custom power systems that meet your specific needs. Vicor Custom Power maintains the flexibility of a small entrepreneurial company while taking advantage of Vicor's technical and business resources to deal effectively with your most challenging power requirements. Vicor has invested in the tools and resources to offer you full service solutions from prototype to mass production with the shortest lead times and the lowest risk.

#### General Capabilities:

- Electrical and Mechanical Design

- Rapid Prototyping

- High Volume Production Capacity

- MIL-STDs Compliance

- Reliability / Certification Testing:

High Temperature Operational Life HALT (Highly Accelerated Life Test) Mechanical / Thermal Shock Vibration Humidity Acceleration Altitude Explosive Atmosphere Temperature Cycling Burn In EMI Transient Immunity

Put Vicor Custom Power to work for you today, call 1-800-496-5570 to speak with a Vicor Custom Power engineer, or email apps@vicorcustom.com

vicorcustom.com

# EMBEDDED SYSTEM

November/December 2009 Volume 5 Number 8

#### **COLUMNS**

#### Field Intelligence

Packet processors to speed and protect military networks

By Duncan Young

#### Mil Tech Insider

9 High-voltage power distribution enhances platform modernization

By John Wemekamp

#### **Legacy Software Migration**

Application modernization provides link between historical systems and contemporary technology

By Bill Errico, Micro Focus

#### **Crosshairs Editorial**

C4ISR and the big picture

By Chris A. Ciufo

#### **DEPARTMENTS**

**Daily Briefing: News Snippets**

By Sharon Schnakenburg-Hess

37 **Editor's Choice Products**

#### **Software:** Static analysis: Beyond the compiler

16 How good is your compiler (at finding coding defects)?

By Wojciech Basalaj, Ph.D., PRQA

#### Hardware: Designing in cool reprogrammability

Releasing the full potential of FPGA-based designs 20 By Rob Evans, Altium Limited

23 Advanced cooling techniques beat the heat for rugged embedded COTS systems

By Ivan Straznicky, Curtiss-Wright Controls Embedded Computing

#### Technology: Battlefield power-up -It's all about the inverter

26 On Board Vehicle Power (OBVP): Mobile power for tomorrow's battlefield By Doug B. Mays, Diversified Technology

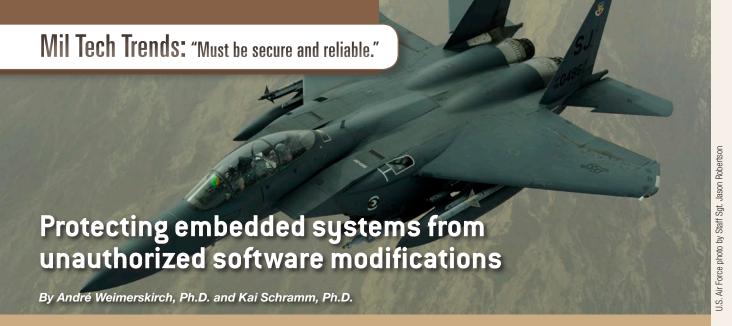

#### Mil Tech Trends:

"Must be secure and reliable."

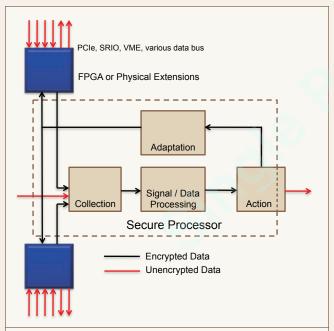

29 Adding trust to an embedded system with a secure anchor point

By J. Ryan Kenny, CPU Tech

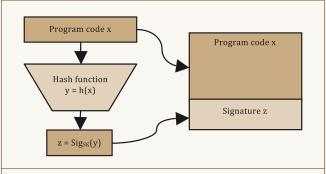

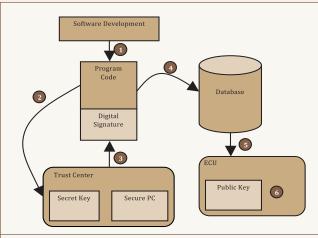

Protecting embedded systems from unauthorized software modifications

By André Weimerskirch, Ph.D. and Kai Schramm, Ph.D., escrypt Inc.

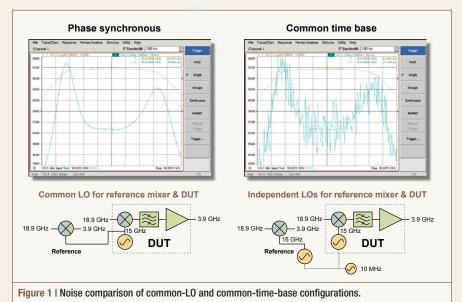

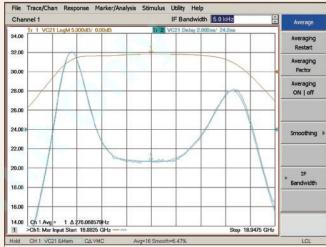

A new approach to testing embedded-LO converters

By David Ballo, Agilent Technologies

#### ON THE COVER:

A P-38J "loaded for bear" dives on a bomb run. The P-38 was innovative and unusual for the 1940s as the twin counter-rotating props provided roll stability over single-prop fighters. First deployed during World War II to the Alaska theater (surprised?), the P-38 had an extended range that provided security to bombers deep into Germany. On the modern COTS-based battlefield, security is afforded by systems that behave in predictable ways and that can't be compromised due to cyber-attack or bad actors. See stories starting on page 29. (Image courtesy of Wikipedia Commons.)

#### **EVENTS**

www.opensystemsmedia.com/events

**Ethernet Technology Summit** February 24-25, 2010 • San Jose, CA www.ethernetsummit.com

#### Published by: OpenSystems media.

ISSN: Print 1557-3222

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2009 OpenSystems Media © 2009 Military Embedded Systems

#### WEB RESOURCES

Subscribe to the magazine or E-letter Live industry news • Submit new products

http://submit.opensystemsmedia.com

#### White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

# Annapolis Micro Systems

The FPGA Systems Performance Leader

# WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

#### **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

#### ADVERTISER INFORMATION

| Page | Advertiser/Ad title                                                                |

|------|------------------------------------------------------------------------------------|

|      |                                                                                    |

| 21   | ACCES I/O Products, Inc. –<br>USB embedded I/O                                     |

| 5    | <b>Annapolis Micro Systems, Inc.</b> – WILDSTAR 5                                  |

| 2    | <b>Ballard Technology</b> – USB powered avionics                                   |

| 19   | CM Computer – CM-SIXHEX                                                            |

| 36   | <b>CPU Technology, Inc.</b> – Acalis Secure Processor                              |

| 27   | Curtiss-Wright Controls Embedded<br>Computing – Reduce your risk                   |

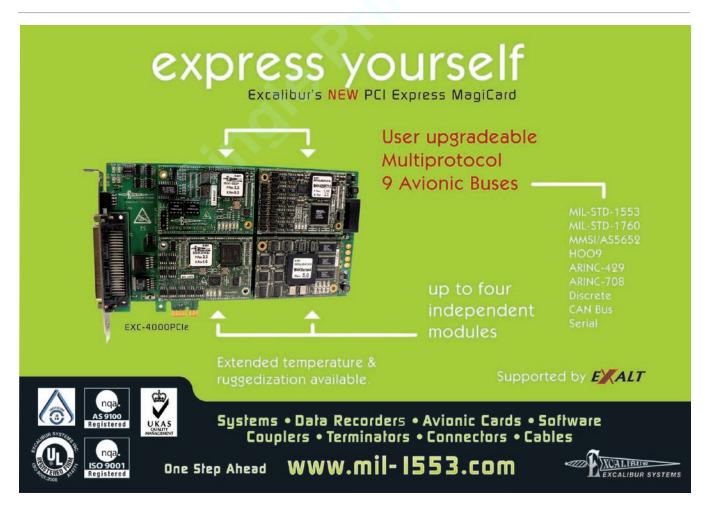

| 13   | Excalibur Systems, Inc. – Express yourself                                         |

| 39   | GE Fanuc Intelligent Platforms,<br>Inc. – Which of these platforms use<br>GE Fanuc |

| 7    | Kontron – We do not build Navy ships                                               |

| 18   | Nallatech – High performance FPGA solutions                                        |

| 25   | North Atlantic Industries – MIL-STD power supplies                                 |

| 40   | <b>Pentek, Inc.</b> – We've hatched the next generation of software                |

| 31   | <b>Phoenix International</b> – Data storage                                        |

| 31   | <b>TEWS Technologies LLC</b> – COTS I/O Solutions                                  |

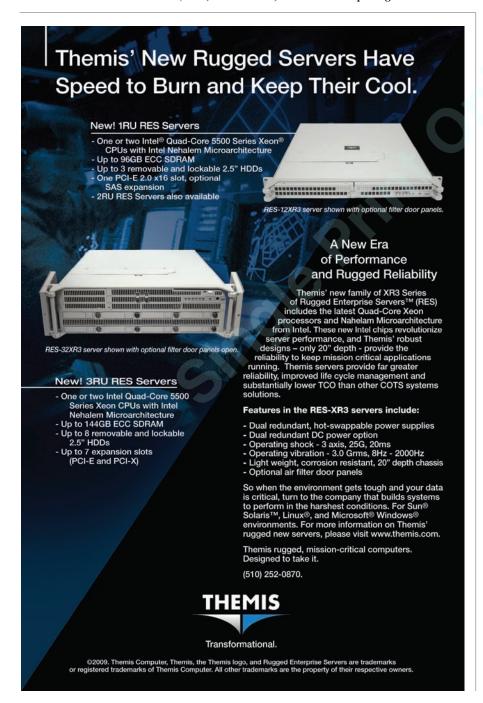

| 12   | <b>Themis Computer</b> – New Rugged Servers                                        |

| 24   | <b>Tri-M Systems Inc.</b> – 100Mhz PC/104<br>Module                                |

| 35   | <b>Tri-M Systems Inc.</b> – PC/104<br>Can-Tainer                                   |

| 17   | Twin Oaks Computing, Inc. –<br>CoreDX                                              |

| 3    | Vicor – Custom power solutions                                                     |

| 28   | <b>VPT Inc.</b> – Efficent, reliable power                                         |

| 10   | White Electronic Designs –<br>We've cleared the board                              |

#### **E-LETTER**

#### www.mil-embedded.com/eletter

- 10 GbE in net-centric warfare: Why commercial network cards can't drive the application By Rob Kraft, AdvancedIO Systems Inc.

- Creating a simulated environment for UAS operator training By Yannick Lefebvre, Presagis

- Protecting today's military electronics systems with real-time hardware/software protection countermeasures By Paul Bradley, DAFCA, Inc.

# Military EMBEDDED SYSTEMS

**DSP-FPGA.com**

PC/104 small form factors

Embedded COMPUTING

#### Military & Aerospace Group

Chris Ciufo, Group Editorial Director cciufo@opensystemsmedia.com

Sharon Schnakenburg-Hess Assistant Managing Editor sschnakenburg@opensystemsmedia.com

Jennifer Hesse, Assistant Managing Editor jhesse@opensystemsmedia.com

Terri Thorson, Senior Editor (columns) tthorson@opensystemsmedia.com

Monique DeVoe, Copy Editor

Hermann Strass, European Representative hstrass@opensystemsmedia.com

Konrad Witte, Senior Web Developer

Steph Sweet, Creative Director

Joann Toth, Senior Designer

David Diomede, Art Director

Phyllis Thompson

Circulation/Office Manager subscriptions@opensystemsmedia.com

#### Sales Group

Dennis Doyle, Senior Account Manager ddoyle@opensystemsmedia.com

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker, Strategic Account Manager rbarker@opensystemsmedia.com

#### Andrea Stabile

Advertising/Marketing Coordinator astabile@opensystemsmedia.com

Christine Long, Digital Content Manager clong@opensystemsmedia.com

#### **International Sales**

Dan Aronovic, Account Manager - Israel daronovic@opensystemsmedia.com

Sam Fan, Account Manager - Asia sfan@opensystemsmedia.com

#### **Regional Sales Managers**

Ernest Godsey, Central and Mountain States egodsey@opensystemsmedia.com

Barbara Quinlan, Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr, Northern California sstarr@opensystemsmedia.com

Ron Taylor, East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

#### Reprints and PDFs

Nan Holliday 800-259-0470

republish@opensystemsmedia.com

#### **Editorial/Business Office**

16626 E. Avenue of the Fountains, Ste. 203 Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystemsmedia.com

Publishers: John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial: Rosemary Kristoff

Vice President Marketing & Sales:

Patrick Hopper

phopper@opensystemsmedia.com

Business Manager: Karen Layman

# » We Do Not Build Navy Ships «

#### Our Customers Do.

At the heart of the most advanced command and control systems deployed in Navy ships are Kontron Military Rugged COTS boards and systems. Keeping us safe with smart applications, military contractors look to Kontron for superior technology, performance and life cycle management expertise.

#### MILITARY RUGGED COTS

Call, Email or Visit today.

Call: 1-888-294-4558

Email: info@us.kontron.com

Visit: www.kontron.com/military

#### Field Intelligence

# **Packet processors** to speed and protect military networks

Commercial network technology will be migrating deep into the digital battlefield to enhance performance, maintain service, and provide a more secure communications environment. Battlefield Network Enabled Capability (NEC) extends from individual soldiers, through Virtual Private Networks (VPNs) in chassis, vehicles, or shelters to the complete command infrastructure. The constant flow of information through shared network-based applications such as situational awareness, voice/data communications, and signals intelligence/surveillance is an essential element of today's sophisticated information-centric warfare environment. To meet the demands for growth, commercial networks employ packet processors to perform a broad range of tasks to manage networks, offload performancesapping tasks such as encryption, and inspect payload content at 10 Gbps line speeds and more.

#### Performance and network security

Just as commercial networks and the military's command and operations network infrastructure require continuous performance growth to meet users' expectations, so do battlefield networks. For example, network-centric applications such as sharing, analyzing, and annotating images from multiple sensors are very demanding of both network and computing resources. These applications can also extend across many tiers of battlefield command and multiple coalition partners with the resultant burden of varying security classifications between the many different systems and participants. The prevention of intrusion and the maintenance of network and data integrity are high priorities.

A common point of vulnerability is the IP address which, if unprotected, can lead to unauthorized access, denial of service attacks, or virus planting. IPsec, which is a mandatory part of IPv6 but only optional for IPv4, provides IP address protection through negotiated message transfers and encryption. But IPsec is not yet universally implemented. Payload content can be further protected with additional levels of encryption that might vary in type with the data's sensitivity. However, the implementation of IPsec, payload security, and the trend for increased line speeds from 1 Gbps to 10 Gbps impose significant additional levels of processing that many subsystems and networks do not have. In addition, changing defense funding priorities means that many legacy fighting vehicles are now being modernized in preference to replacement, introducing many of the capabilities developed specifically for participation in the NEC environment.

#### Packet processing

To meet the needs of network performance and security, packet processors can offload many of the protocol processing layers. And because of their performance potential, packet processors can perform many additional network management and security operations at line speeds. Packet processing provides the performance and capability for perimeter defense, encryption/decryption, virus checking, IP routing and address translation, and detection and prevention of service attacks within embedded computing subsystems, switches, and routers. However, packet processors are also able to analyze the payload content, even at Gbps line speeds, known as Deep Packet Inspection (DPI). DPI can determine the packet type such as voice or data, e-mail, or security threat and includes sophisticated pattern matching to identify packets that might require further processing before dispatch.

These requirements for packet processing have spawned a new generation of high-performance, multicore processing devices based on, for example, PowerPC (Freescale Semiconductor) and MIPS64 (Cavium Networks) cores. These Systemson-Chip (SoCs) offer from 4 to 16 processor cores with GHz clock rates, on-chip pattern matching and security engines,

high-bandwidth memory interfaces, and flexible multi-GHz connectivity options to host processors and networks. GE Fanuc Intelligent Platforms has adopted Cavium Networks' OCTEON packet processing devices and software to power a range of commercial, standardsbased telecommunications products. For military applications requiring extended environmental performance or conduction cooling, VPX (VITA 46) provides the ideal platform for implementations in either 3U or 6U formats. Depicted in Figure 1 is the NPA-58x4, a 4-port GbE AdvancedMC packet processor based on the Cavium OCTEON, transforming into reality the idea that efficient real estate, performance, and functionality could be achieved based on a 3U VPX militarygrade product.

Figure 1 | NPA-58x4 AdvancedMC module from GE Fanuc Intelligent Platforms

GbE is widely implemented and well supported by an ecosystem of multiple vendors of embedded computing equipment including SBCs, switches, routers, software, backplanes, and packaging standards suitable for use in military vehicles. These embedded systems will migrate through 10 GbE and 40 GbE for copper backplanes to the 100 GbE fiber standards of the future. Offloading protocol stacks, maintaining network integrity, and establishing secure zones, media gateways, and firewalls without compromising embedded system performance are key application areas that packet processing is set to benefit.

To learn more, e-mail Duncan at young.duncan1@btinternet.com.

## Mil Tech Insider

### High-voltage power distribution enhances platform modernization

By John Wemekamp

The new generation of ground-based vehicles has moved away from the traditional 28 VDC power generation and distribution systems to high-voltage systems of typically 610 VDC, achieving great savings in space, weight, cost, and efficiency. Although easier to implement on new vehicle designs, high-voltage technology and many of its component parts can also be introduced into existing vehicles to great effect - without the whole scale and potentially disruptive replacement of every 28 VDC powered electromechanical or electronic subsystem. Modernization programs aim to improve the warfighter's operational effectiveness and survivability.

The continued presence of North Atlantic Treaty Organization (NATO) partners in areas of conflict has, for many nations, shifted combat doctrine and drained budgetary resources away from new large-scale ground vehicle procurement programs. Instead, life extension and modernization of existing fleets of armored vehicles is proposed – providing enhanced crew survivability – to add more firepower, increase situational awareness by introducing more Network Enabled Capability (NEC), and reduce maintenance and life-cycle costs. The recent rounds of rationalization, typified by the manned ground vehicle elements of Future Combat Systems (FCS), will result in the migration of new technologies into a series of phased modernization and update cycles for the current armored vehicle fleets to meet these objectives.

#### Mixed high- and low-voltage power systems

Significant weight, space, and efficiency gains will be achieved even by the partial adoption of new high-voltage power systems. Much of the new electrical technology is high-voltage based, whether power generation, distribution, all forms of motion control, driver control, or environmental controls. Modernization initiatives to infuse this technology into older vehicle types will result in two scenarios:

- Change out of the power-generation system to the new high-voltage standard plus the introduction of some new high-voltage subsystems along with the retention of legacy 28 VDC subsystems.

- Continue to generate power at 28 VDC but introduce some new technology subsystems requiring high voltage.

Both scenarios will utilize new power conversion technology between high voltage and 28 VDC or vice versa plus the inclusion of side-by-side distribution and switching systems.

Where and how this power conversion takes place will have a vital impact on a vehicle's weight and space available for other equipment. A large armored vehicle such as a Main Battle Tank (MBT) might require 100+ kW power generation capability. At 28 VDC, this equates to 3,500 A to be distributed around the vehicle, requiring heavy cables and massive switchgear. Obviously, using a higher voltage reduces the current, allowing smaller, lighter cabling and switchgear. But crew safety also becomes a consideration, requiring additional physical protection of cables and connectors as well as the inclusion of ground fault detection circuit breakers.

#### Motion control

Motion control is one of the greatest consumers of power in an armored vehicle. Its applications range from the operation of hatches, fans, and pumps, to the environmental control of workspaces and electronic equipment, to a complete turret assembly. By providing a multi-axis stabilized platform for weapon, sensor, and crew systems, a typical turret system can require tens of kW per axis to control. The new generation of smart Servo Motor Controllers (SMCs) offers more opportunities for reducing weight and space. By providing high-power, three-phase synchronous output to the motor, an SMC can be directed to perform complex, preprogrammed movements by commands received via dual-redundant control buses such as CANbus or Ethernet.

Using solid-state switching and microprocessor technology, these SMCs offer increased reliability plus an inherent capability for sharing diagnostic and future prognostic results with other vetronics subsystems. Curtiss-Wright Controls Electronic Systems has played a major role in the development of equipment and

installation technology for high-voltage ground vehicle power distribution, in addition to switching and motion control systems. Illustrating this breadth of expertise is a family of rugged, highefficiency SMCs, packaged as Line Replaceable Units (LRUs) for vetronics applications, shown in Figure 1. Such an SMC can deliver two axis controls at up to 23 kW per axis in a package weighing only 22 lbs.

Figure 1 | Curtiss-Wright Controls Electronic Systems' family of rugged, high-efficiency SMCs, packaged as LRUs for vetronics applications.

Inserting high-voltage power technology into existing vehicle fleets will undoubtedly create significant savings in weight, space, and efficiency. However, careful trade-offs will be needed to ensure the optimum savings and benefits, particularly as phased introductions of new technologies into each vehicle type are proposed. This will require a deep understanding of each vehicle's power infrastructure, its EMI characteristics, future upgrade plans, and crew safety requirements to create each optimal solution set.

To learn more, e-mail John at john.wemekamp@curtisswright.com.

# We've cleared the board.

# It's your move.

Space-saving system-in-a-package and multi-chip solutions from White Electronic Designs free up board space to make room for your big ideas.

Try our new DDR2 SDRAM that packs 1 GByte into a SnPb BGA package less than 1/2 in<sup>2</sup> ... or our new embedded SLC NAND flash BGA that has the performance of a solid state disk drive in a form factor that is one-fourth the volume of a comparable compact flash-based product.

WEDC lean microelectronic solutions are designed to solve component incompatibilities, reduce design complexity, and extend product life and environmental performance in military applications. We offer turnkey design, assembly and test of custom multi-chip solutions and a wide range of standard military off-the-shelf space-saving solutions.

Expand the possibilities; explore your options at www.whiteedc.com/move.

602.437.1520 TEL | 602.437.9120 FAX

During an era when battlefield technology is rapidly evolving, the DoD's goal is to ensure that the warfighter is equipped with best-of-class, mission-critical technology. Despite the need to stay ahead of the technology curve, the government's budget cycle can sometimes be out of sync with these objectives. Through application modernization, however, COBOL applications can be extended into new environments, enabling agencies to leverage the benefits of modern technologies such as Web and Service Oriented Architecture (SOA) enablement, and cloud computing.

Despite the recent push toward modern programming languages like Java and C++, the majority of government agencies still rely on COBOL for their missioncritical applications. One of the primary reasons COBOL still exists is because many decades of time and millions of dollars are often invested in DoD applications. Aside from the fact that rewriting applications with a more modern programming language, or replacing them completely, puts operability of the applications at risk, COBOL still provides real value to the agencies and organizations it serves. Because of the programming language's longevity, the systems have evolved with defense agencies and continue to perform missioncritical tasks in support of the warfighter efficiently and reliably, providing every reason for the DoD to keep these historical systems alive.

#### Modernization enables Web capabilities

Integrating modern technologies with the 50-year-old COBOL programming language, however, is no simple feat. As network-centric warfare becomes more dependent on Web capabilities for enhanced availability and streamlined logistical processes, upgrading critical applications for Web compatibility is a must.

Application modernization fosters communication between historical systems and contemporary technologies, while preserving the unique value encompassed in existing IT systems. A compelling alternative to rewriting or replacing critical applications, modernization is often deployable in less than two months, enabling a rapid response to mission changes and quick realignment of current applications in compliance with constantly evolving security requirements

Integrating modern technologies with the 50-yearold COBOL programming language, however, is no simple feat. As network-centric warfare becomes more dependent on Web capabilities, ... upgrading critical applications for Web compatibility is a must.

and federal regulations. Modernization can also save agencies millions of dollars, and in many cases reduces operating costs by up to 80 percent. As the applications often reflect the investment of innumerable resources and years of code modified to meet the specific demands of individual agencies, changing the code can put operability in jeopardy. However, modernization eliminates the risk factor because it does not require the alteration of a single line of code. Instead of altering the code, the server emulates a mainframe execution environment, working with the target operating system to allocate memory for the historical application.

#### The shift toward cloud computing

As agencies government-wide are starting to turn to modern technologies like cloud computing for enhanced availability and efficiency, defense agencies that rely on historical systems can be quick to follow through the use of modernization. Modernizing critical applications using Service Oriented Architecture (SOA) provides agencies otherwise bound to the mainframe environment the ability to leverage these modern technologies. Inserting an added layer of wrapper code that enables access to business functions, COBOL applications can now operate in a Web 2.0 environment, providing a responsive and rich Internet application, using unchanged code. The now-Webbased applications maintain the same functionality as when tied to the mainframe. Business regulations might have moved platforms with a Web 2.0 interface added, but quality assurance testing time is ultimately reduced because the application business logic remains untouched.

Security risks are often cited as the number one concern when upgrading systems for cloud computing compatibility. Government agencies concerned with a loss of control over the environment in which the applications are executing can still leverage the benefits of cloud computing by taking practical steps toward the cloud, without making the full commitment. One solution is to transition applications to a private cloud, providing the same Web benefits from within the boundary of an agency's own firewall. A private cloud enables agencies to leverage benefits such as pay-as-you-go licensing and elasticity, from within their own data centers, at their own pace.

As government agencies continue to shift toward cloud computing, historical systems do not need to act as a barrier to defense agency modernization. Implementing modernization solutions allows defense agencies to leverage the benefits of modern technologies such as cloud computing, SOA, and Web-based technologies, ultimately providing the warfighter with more advanced battlefield technology at a faster time-to-deployment.

Bill Errico is vice president of federal sales and marketing at Micro Focus. He can be contacted at Bill.Errico@microfocus.com.

# Daily Briefing: News Snippets

By Sharon Schnakenburg-Hess, Assistant Managing Editor

www.mil-embedded.com/dailybriefing

#### **3U CompactPCI joins U.S. Army ranks**

Following the trend of an increasing number of 3U (and sometimes even smaller) form factors enlisting for duty, prime Northrop Grumman recently marshaled yet another ware for the U.S. Army's Small Tactical Airborne Radar (STARLite) synthetic aperture radar (Figure 1): BittWare's GT-3U-cPCI (GT3U) ruggedized 3U CompactPCI board. The agreement stipulates delivery of an unquantified "large production order" of the GT3U hybrid signal processing boards, which are powered by an onboard Altera Stratix II GX FPGA and a group of four onboard ADSP-TS201S TigerSHARC DSPs for flexibility. The boards will provide STARLite's "high-end" signal processing, which combines numerous radar images into a single high-res image, with the goals of target coordination and unprecedented situational awareness for ground-troop protection plus increased surveillance capabilities.

Figure 1 | STARLite synthetic aperture radar image of Fort Huachuca facilities, courtesy of Northrop Grumman

#### **RFID system spins 'military** technology'

The phrase "military technology" often conjures mental images of warfighters' battlefield wares. However, the Marine Corps Base Camp Pendleton (MCBH) is giving the phrase a slightly different spin, thanks to a Web-based RFID tracking system by 3M, slated to enable Anchorage's Alaska National Guard and MCBH in more efficiently managing 40,000+ personnel records. The result: a projected accuracy increase plus a man-hour decrease equating to about \$1.5 million per year. The primary catalyst: 3M's File Tracking Software V3.0, proven at the recent Marine Corps Base Hawaii's pilot RFID project and used with 3M's D4 RFID tag. File Tracking Software V3.0 supports Windows Vista and offers Internet reporting and locating capabilities that render it usable on any Web-browser-enabled computer. Consequently, custom reports and item lists are easily generated, and personnel can be more rapidly reassigned or deployed.

#### RATS welcome on the battlefield, by way of Android

While cell phone manufacturers and consumer gadgeteers were the first to appreciate Google's Android mobile operating system, defense industry pundits have been quite reluctant about its battlefield suitability. However, a combat-savvy incarnation of Android has emerged as the Raytheon Android Tactical System (RATS). RATS renders fast delivery of multimedia content such as full motion video and images to warfighters, via intelligence data dissemination utilizing RATS' Distributed Common Ground System (DCGS) Intelligence Backbone (DIB) system architecture. The benefit: DIB content viewing can take place immediately and can be searched by other mobile device users, enabling decision-making within seconds instead of hours. RATS "widget" applications in development are biometric collection including facial recognition, in addition to streaming video camera feeds and license plate reading, Raytheon reports. Rest assured, "some lightweight encryption" will be enabled, as will even more features, Forbes reports. (See Raytheon Sends Android To Battlefield, www.forbes.com/2009/10/19/androidgoogle-military-technology-wireless-raytheon.html)

#### First OpenVPX contract?

At the speed of light, it seems, the once-controversial OpenVPX Industry Working Group has very recently (and very peacefully) surrendered its recommended VPX system interoperability specification back into VITA/VSO's hands by way of VITA 65. And only a proverbial minute later ... Mercury Computer Systems, who spearheaded the OpenVPX (Figure 2) effort, has already announced "a multimillion-dollar system order from a leading defense supplier" for Mercury's OpenVPX wares. The unnamed defense supplier will utilize various technologies within Mercury's (OpenVPX) Ensemble 6000 Series for a global radar update. The deliverable: signal processing tucked inside a heterogenous environment within an overarching infrastructure of robust systems management. The pace: Fast. Mercury's support and services for complete subsystem development, validation, and qualification will comply with the defense supplier's Quick Reaction Capability (QRC) requirement: Integrated OpenVPXbased architecture delivery within 10 months (at most) and low-rate initial production in fewer than 16 months.

Figure 2 | Within days of the OpenVPX Industry Working Group sending its recommendations to VITA/VSO, Mercury announced a "multimillion-dollar system order from a leading defense supplier."

#### U.S. Army signs a 'fitting' contract

The U.S. Army recently put pen to paper for a \$19 million Land Warrior maintenance contract with General Dynamics C4 Systems, which stipulates a year of "maintenance" for the presently-in-combat, modular, integrated Land Warrior fighting system ensembles (Figure 3). The team-leader-level ensembles include a small computer that heightens navigation and situational awareness capabilities, a helmet-mounted display, and a radio connectivity headset. Meanwhile, provided under the contract are logistics support and comprehensive engineering, in addition to maintaining returning-from-theater and training ensembles. The contract also affords two option years, which could boost the contract's value to \$50 million. The contract's inanimate beneficiaries are the U.S. Army's 300 kits for vehicle integration, along with 900 Land Warrior ensembles and associated Land Warrior equipment.

Figure 3 | A Land Warrior fighting system ensemble, photo courtesy of General Dynamics C4 Systems

#### Common thread woven among Navy subs

The 109-year-old U.S. Navy submarine force is nothing if not diverse, considering its lineup of SSBN fleet ballistic missile submarines, its SSGN guided-missile submarines, and its SSN attack submarines. But what is the common thread amongst all U.S. Navy subs? They will all soon sport the capability of two-way, real-time communications with surface ships, landbased assets, and aircraft - minus the requirement to emerge to periscope depth – as part of the U.S. Navy's Communications at Speed and Depth (CSD) program. Having successfully completed a recent CSD Preliminary Design Review (PDR), prime Lockheed Martin plans to reach fait accompli by providing a triad of types of two-way communications buoys plus associated submarine accoutrements and shore equipment. Two genres enable UHF and Iridium satellite transmission, while the third consists of an aircraft- and submarine-launchable acoustic-to-RF gateway system.

For consideration in Daily Briefings, submit your press releases at http://submit.opensystemsmedia.com. Submission does not guarantee inclusion.

Figure 4 | U.S. Air Force officials at Germany's Ramstein Air Base recently said goodbye to their final C-130E Hercules, U.S. Air Force photo by Airman 1st Class

#### C-130E says 'goodbye' ... and 'hello'

U.S. Air Force officials at Germany's Ramstein Air Base recently bid a fond farewell to their final C-130E Hercules (Figure 4). The C-130E then flew to its new home – the Powidz Air Base in Poland - per a Foreign Military Sales lease agreement between Poland and Air Force Materiel Command, signifying three primary milestones: 1) The C-130E's conclusion of about 40 USAF service years; 2) a new era for the Polish air force, which previously used the CASA C-295 twin turboprop as its primary aircraft for tactical transport (CASA C-295 can accommodate 70 passengers or 7.5 tons, while the more cargo-savvy C-130E can heft a 17-ton payload or 90 fully equipped passengers); and 3) the United States' transition to the updated and upgraded C-130J, featuring automation and computerization so advanced that the navigator and flight engineer positions have, consequently, been eliminated.

#### Seeing the light ... in tunnels, behind walls

Did you see that? Odds are good that the answer is a resounding "no" when an object is located within a tunnel or behind a wall. However, the answer has now changed to "yes," courtesy of a phase II Department of Army contract with TiaLinx, Inc. The contract affords continued development of a V-band miniature antenna array to be integrated into TiaLinx's Eagle60 Ultrawideband (UWB) Radio Frequency (RF) imaging systems. The systems utilize advanced mm-wave RF distributed sensors to enable users to even see movement of live objects within tunnels or behind walls (Figure 5), provide visual detection of landmines or unexploded ordnances, and render land, sea, and air surveillance in smog, rain, and fog.

Figure 5 | A new V-band miniature antenna array means users can even see movement of live objects within tunnels or behind walls.

Many believe that if source code compiles cleanly, with all warnings activated, then it is ready to move on to a verification stage such as test or code review. However, it is dangerous to assume that if the code has compiled cleanly, then any errors present must have resulted from the interpretation of the requirements and not their implementation. Wojciech empirically evaluates this assumption and proves that the range of warnings provided by any compiler is extremely limited when compared to those produced by a dedicated static analysis and Coding Standards Enforcement (CSE) tool.

It is a commonly held view that if source code compiles cleanly, with all warnings turned on, then it is ready for verification such as test or code review. The danger with this assumption is that if the code has compiled cleanly, then any errors present must be in the interpretation of the requirements and not in their implementation. However, an empirical evaluation of this assumption ultimately shows that the range of warnings provided by any compiler is seriously limited when compared to those produced by a dedicated static analysis and Coding Standards Enforcement (CSE) tool.

The comparisons made herein use the GNU Common C++ "2" version 1.6.3, a realworld code base of around 42,000 lines of code. As this is a cross-platform library, it does not favor any particular compiler and can be used as a representative sample that any compiler might be expected to handle. Its modest size allows all compiler warnings to be manually reviewed for their accuracy, while ensuring at the same time that their diversity and amount is non-trivial.

The four compilers examined are GCC, Visual C++, C++Builder, and Intel C++ Compiler, along with a static analysis and CSE tool to show that if developers rely too heavily on their compiler to identify coding defects, they might find that their code isn't maintainable, reusable, or portable. In addition, Visual C++ "Team edition" supplements its standard compiler warnings with a "code analysis" feature, the output of which is included in these results.

#### Warning outputs generated

In practice, every one of the defects missed by one of these four compilers has an impact on the quality of the code base, be that in its maintainability, portability, or reusability. That represents a significant threat when deploying the code, despite the fact that the majority of the sample source code passes the compilers' architected checking parameters.

As these compilers are based on different front-ends, different warnings can be anticipated from each. Table 1 presents a sideby-side comparison of distinct warnings generated by each compiler, and by the static analysis tool, for the code base used in our comparison: GNU Common C++ "2". The latest version of each compiler available at the time our results were compiled was used with the maximum warning level enabled. (The header row of Table 1 indicates the exact compiler versions and options used.) Rather than benchmarking these compilers relative to one another, their warning outputs were compared with a static analyzer for C++.

As indicated in the last row in the table, the CSE tool generates in excess of 400 warnings, while none of the compilers tested even manage to return 20. In fact, static analysis is empirically shown to identify 25 times more warnings than the best among all four compilers - Visual C++ with Code Analysis enabled (/analyze option). It is interesting to note that without this feature enabled, Visual C++ generates the fewest warnings among all the compilers tested.

The first column of data in Table 1 shows the percentage of warnings generated by each compiler that were also detected by the static analysis tool. Note that the degree of overlap is high, with an average

|                           | PR                         | GNU                   | Microsoft     | Microsoft       | CodeGear       | Intel           |

|---------------------------|----------------------------|-----------------------|---------------|-----------------|----------------|-----------------|

|                           | Static<br>Analysis<br>Tool | GCC                   | Visual<br>C++ | Visual<br>C++   | C++<br>Builder | C++<br>Compiler |

|                           | 2.5                        | 4.3.2                 | 2008          | 2008            | 2009           | 11.0.066        |

| Overlap                   | all checks                 | -W -Wall<br>-pedantic | /W4           | /analyze<br>/W4 | All warnings   | /W4             |

| GCC warnings              | 88%                        |                       |               |                 |                |                 |

| VC++ /W4 warnings         | 100%                       |                       |               |                 |                |                 |

| VC++ /analyze warnings    | 73%                        |                       |               |                 |                |                 |

| C++Builder all warnings   | 92%                        |                       |               |                 |                |                 |

| Intel C++ /W4 warnings    | 67%                        |                       |               |                 |                |                 |

| ISO C++ conformance       |                            | 17%                   | 11%           | 11%             | 11%            | 11%             |

| Portability problems      |                            | 0%                    | 0%            | 0%              | 6%             | 0%              |

| Design problems           |                            | 1%                    | 2%            | 7%              | 3%             | 2%              |

| Local standards           |                            | 0%                    | 0%            | 10%             | 0%             | 0%              |

| Efficiency and use of C++ |                            | 0%                    | 0%            | 0%              | 0%             | 0%              |

| Maintainability           |                            | 3%                    | 3%            | 3%              | 5%             | 4%              |

| Coding style              |                            | 2%                    | 0%            | 0%              | 0%             | 3%              |

| Average overlap           | 84%                        | 3.1%                  | 2.4%          | 4.4%            | 3.6%           | 2.9%            |

| Distinct warnings         | 412                        | 8                     | 7             | 16              | 12             | 13              |

Table 1 | Default detection comparison - The basis of comparison and each percentage figure is the ratio between distinct warnings reported by a compiler and a static analysis tool within a given category. The header row details the exact compiler versions and options used to enable the maximum warning level.

84 percent of compiler warnings replicated by the CSE tool. This side of the comparison is only given for completeness, as developers would be expected to enable compiler warnings regardless of whether or not static analysis is performed.

The remaining rows of Table 1 show the other side of the comparison: How much of what is statically detectable do compilers flag? It is evident that compiler warnings steer clear of the "Efficiency and use of C++" category. This is expected, as compiler optimizations are performed in the back-end, typically silently. However, it is worth noting that dedicated CSE tools have a range of checks in this category focused on inefficient design, which cannot be corrected automatically, unlike low-level compiler optimizations.

#### Common warnings missed

Portability is a common warning category missing from a compiler's arsenal. Only C++Builder generated a single warning that can be classified as a portability issue, compared to 17 flagged by the static analysis tool. These represent those constructs that comply with the ISO C++ Language definition but can cause problems with different compiler implementations. It is not uncommon for compiler vendors to lock developers in by offering

extensions to ISO C++, and it is unsurprising that portability is not high on the agenda for them. This represents another aspect of portability concerns, conformance to ISO C++, which is addressed by a separate warning category in the static analysis tool.

To most compiler vendors, ISO C++ compliance boils down to accepting as much valid C++ code as possible, while sidestepping the issue of detecting non-conforming code - often their own language extensions. Detecting ISO C++ non-conformance is one of a CSE tool's strengths, which is evident from Table 1. It is apparent that most compiler warnings can be classified as (code) "Design Problems" and "Maintainability," with some so minor as to merit them being demoted to style issues. However, even for these focus areas, the coverage compared to the static analysis tool is far from comprehensive, standing at 7 percent for the best contender - Visual C++ with code analysis feature.

Other warning categories that compilers traditionally avoid include: naming conventions, code layout, complexity metric thresholds, and banning certain keywords (for example, throw) and functions (for example, malloc), with a notable

#### **Big Performance** in a Small Package

Need a flexible, openarchitecture communications infrastructure?

Concerned about data interoperability?

Struggling with constrained resources?

Save time and money by using a proven, interoperable communications middleware solution.

CoreDX provides a robust, quality-of-service enabled Data Distribution Service. Our implementation is perfect for embedded systems with constrained resources and a need for high-throughput, low-latency communications.

Integrate CoreDX today and launch your product.

Try the FREE CoreDX evaluation today!

www.twinoakscomputing.com

exception of a Visual C++ code analysis feature that has hardwired warnings for use of \_alloca, \_snprintf, and TerminateThread functions. As this is not as comprehensive as the static analysis tool's configurable check that allows any function to be specified, half a point was awarded, giving this compiler a score of 10 percent for Local (company specific) Standards enforcement. The primary benefit of enforcing the aforementioned areas is enhanced reusability of code, and it is apparent from Table 1 that this is virtually untapped by compilers.

| Coding standard<br>enforcement                         | Static<br>analysis tool | GCC   | Visual<br>C++ | VC++ /<br>analyze | C++<br>Builder | Intel<br>C++ |

|--------------------------------------------------------|-------------------------|-------|---------------|-------------------|----------------|--------------|

| HICPP violations detected                              | 16399                   | 3     | 33            | 42                | 40             | 63           |

| JSF++ violations detected                              | 33968                   | 3     | 23            | 26                | 41             | 43           |

| MISRA C++ violations detected                          | 9082                    | 25    | 70            | 72                | 76             | 67           |

| Average overlap with static analysis tool              |                         | 0.10% | 0.35%         | 0.38%             | 0.40%          | 0.42%        |

| Table 2   Coding Standard Enforcement (CSE) comparison |                         |       |               |                   |                |              |

When comparing the actual warning instances produced by each tool, it would not be particularly enlightening to tabulate raw warning counts, so common C++ Coding Standards will serve as an objective basis of comparison instead. As can be seen from Table 2, none of the compilers offer any noticeable enforcement of High Integrity C++, JSF++, or MISRA C++, compared to the violations recorded by the CSE tool.

#### **CSE tool: Most comprehensive/** transferable route

It is a common misconception that compiler warnings are a sufficient means of statically analyzing source code. The range of warnings available from marketleading compilers is limited compared to a dedicated static analysis and CSE tool like PRQA's QA•C++. Moreover, the few checks that are available tend to be focused on code misbehavior and maintainability problems, with reusability and portability issues completely overlooked. A dedicated CSE tool offers comprehensive enforcement of all of these areas, while remaining compiler agnostic, so that code bases and development environments do not have to be tied down to a particular compiler and platform.

Dr. Wojciech Basalaj has nine years of technical experience with PRQA in the Consulting Services Group and is the most senior Technical Consultant.

Wojciech graduated from King's College, London with a First Class BSc degree in Computer Science in 1997. As part of the course, he undertook a oneyear industrial placement at Lucent Technologies Wireless in Winchester, UK. Wojciech obtained his Ph.D. in the field of Information Visualization at Trinity College, Cambridge. He can be contacted at Wojciech\_Basalaj@ programmingresearch.com.

**PRQA** 617-273-8448 www.programmingresearch.com

# HIGH PERFORMANCE FPGA SOLUTIONS RUGGED EMBEDDED VXS & XMC SOLUTIONS PowerPC & Dual FPGA VXS compute cards Analog & Digital I/O and FPGA processing XMC mezzanines Processing and I/O for SigInt Radar and SDR applications Rugged solutions to support multiple target applications FPGA MINIATURIZED intel Nallatech Inc. Toll Free: I-877-44-NALLA contact@nallatech.com www.nallatech.com

© 2009 Nallatech Inc. All Rights reserved. All trademarks or registered trademarks are the property of their respective owners

#### VPX, VME & cPCI True Military ATR Enclosures

#### Fly first class with CM Computers

We are conscious that not all military integrators will require a top class ATR chassis like our new SixHex series, but we can ensure that our fortunate customers will enjoy the experience.

It has been demonstrated in the field that ATR enclosures are crucial to your end system reliability and performance. Therefore we have developed a superior product to guarantee that your payload electronics are matched with excellence.

#### The perfect Sealed COTS solution for advanced military electronic systems

Breaking all limitations previously understood by chassis designers, our fourth generation Six Heat Exchanger ATR series meets the demand for high power solutions that require exceptional thermal performance and truly flexible system integration.

The SixHex is manufactured incorporating US military standard components throughout.

#### **Product Highlights**

- Contaminant-free enclosure

- Available in 1/2, 3/4 & 1 ATR size

- VPX, VME & cPCI ready

- Accepts Conduction & Air-cooled 6Us

- Flexible top & bottom I/O wiring

- Integrated Temperature Control Unit

- Six internal Heat Exchangers

- Up to 1.8 KW total Power Dissipation

- Up to 150 W per slot

- Dramatically increases payload MTBF

- 2 User defined PSU DC outputs

- 20°C less than heat exchanger ATRs

- 45°C less than conventional ATRs

- Stand alone low weight solution

- Customizable to specific requirements

- Mounting Tray with quick release system

All our chassis products are delivered Tested and Certified by independent authorized Labs per MIL-STD-461E & MIL-STD-810F for immediate deployment in US Navy & US Air Force military Fighters and Helicopters.

CM Computer SixHex: Pure Power, Pure Dissipation, Pure Thermodynamics

Visit www.cmcomputer.com or contact us at info@cmcomputer.com to request our Chassis Catalog

For all the power and flexibility FPGAs bring to embedded designs, the additional development process injects new levels of complexity and constraint into the design workflow. Unifying the conventional hardware-FPGA-software design processes to make full use of FPGA reprogrammability is one way forward.

As FPGA technology barnstorms its way through the military electronics and systems and virtually all other sectors of the embedded electronics industry, applications exploiting the advantages of programmable logic are becoming a mainstay. Communications, airborne, and control systems in particular benefit from the design flexibility, field reconfiguration, and parallel processing capabilities of FPGAs, while the short design cycle and simpler verification process help to get applications into the field faster.

In spite of the FPGA's pervasiveness, though, very few applications are truly harnessing the FPGA's full potential for flexible design. This limitation results from the fact that FPGA development has simply been added to, or at best bolted on to, the traditional software-hardware workflow. This isolated FPGA development stage adds significant complexity to the overall design process.

To simplify the overall undertaking and restore design choices, the individual design processes - hardware design, software development, and programmable hardware design - need to be brought together so they can be tackled as a single task. If this is implemented at a fundamental level where all the processes

share a single pool of design data and common design environment, the dominant and unique advantage of FPGAs reprogrammability - can be used to advance FPGA-based designs to the next level. Key to harnessing the full flexibility of FPGAs is an understanding of their evolution, design challenges, and what can be done to restore harmony among the three major FPGA-containing system design aspects: hardware, programmable hardware, and software.

#### FPGAs evolve from glue logic to SoCs

Upon entering the embedded market, FPGAs were first regarded as a convenient and efficient host for implementing large sections of "dumb" glue logic for which development need not involve or interact with other elements of the design process.

However, FPGA devices, and how they are used, have significantly evolved from the concept of convenient containers for mass digital logic. High-capacity FPGAs now host entire SoC designs, where core functional elements such as processors, memory, and high-speed data processing are implemented in the programmable space. In military embedded systems where the relatively low production runs

struggle to justify a new ASIC start, FPGAs provided a viable, cost-effective path forward for harnessing the physical simplicity and reliability benefits of an SoC approach.

Compared to simple glue-logic designs, a major difference with SoC implementations is that software and hardware development are now fundamentally bound to, and dependent upon, the FPGA design. This is because FPGA devices and support peripherals are the center and core elements of the physical design, and the embedded application software is hosted within the FPGA space. As a result, any change in the FPGA domain will have a significant effect on the hardware and software domains.

#### Restrained innovation

Regardless of the interdependence between design domains, the conventional development process for an FPGA-based product design still reflects a traditional approach by regarding each part of the design (hardware, software, and now embedded hardware) as separate, disconnected tasks.

A change in one domain tends to lead to a disruptive, time consuming redesign in the others. This means that major decisions such as hardware-software partitioning must be made (and locked in) early in the design cycle - just as they were with traditional "non FPGA-based" embedded designs. In practice, physical hardware (FPGA devices and peripheral hardware) and then programmable hardware elements are locked down, in sequence, before meaningful software development can proceed.

Those initial decisions define the parameters and constraints for subsequent development processes, so the design options are increasingly limited through each sequential process. For example, the selected FPGA device (and hardware peripherals) will define a performance ceiling that includes identifying which embedded IP can be implemented. In turn, the embedded hardware design will define the functional capabilities available to the software. Or it could be as simple as the FPGA device only supporting soft processors supplied by that device vendor, which in turn defines the programming options available to the application software.

Additionally, pursuing concepts like fine tuning a design's performance by moving software algorithms into embedded hardware, changing from an embedded to hardwired processor, or opting for a different FPGA device type will force a substantial redesign in all domains hardware, programmable hardware, and software. For mil/aero systems development where hard deadlines are mandatory, the resulting design cycle disruption is untenable, so most engineers avoid tackling this type of design exploration at all costs. Yet invariably, high performance and design stability are also paramount, so investigating processor options and the potential benefits of softto-hard algorithm transfers is essential.

#### Restoring unity

As mentioned, simply adding the FPGA development process on to the existing design workflow constrains the ability to harness its full flexibility potential. In applications where the low NRE costs and rapid design are of particular advantage, the barriers imposed by conventional design processes are diluting those attributes. Yet this is just where FPGAs should be exploited to maximum effect.

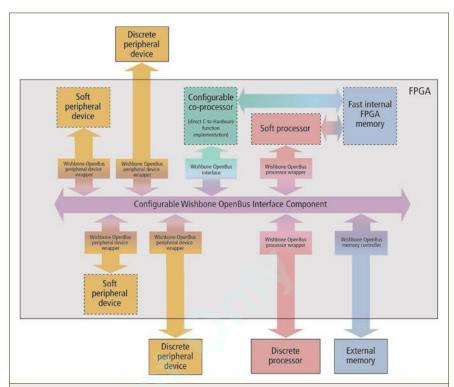

The first step to restoring design choices and fully harnessing FPGAs is to bring the design processes – hardware design, software development, and programmable hardware design - into one sphere (Figure 1). By using a single design system

Figure 1 | The full potential of FPGAs can be harnessed when embedded hardware development, physical hardware design, and software development all exist in a single, fundamentally connected design environment.

and application that draw from a single data model of the entire design, the design domains can interact and respond when design changes are made in an individual domain. In practice, each domain is using a subset of the same design and component library data. As a result, design changes such as moving functions between software and hardware or exploring alternative devices are simplified, since a change can easily (or even automatically) be reflected through all the domains.

The design data and configuration files for the selected FPGA device, for example, are available to both the hardware and FPGA design domains, from the single pool of design data. If the FPGA device or its pin configuration is changed in the FPGA design space, that information is immediately available for implementation in the hardware design space. The action of exploring design options is more practical, while higher-level design functions like swapping pins between the hardware and FPGA design domains are simplified.

#### **Exploiting reprogrammability**

In this singular design environment, developers can finally start to fully harness the flexibility of FPGAs. Take a typical situation where the most practical placement of physical hardware components creates extremely complex FPGA-to-peripheral connectivity, in part due to high-density BGA packaging. One answer is to bring the parts of that routing complexity inside the FPGA itself, by making strategic board connectivity paths via the FPGA's reassignable pins and internal routing.

Here, the FPGA's pin reassignment and internal routing capabilities are used to solve a board routing challenge, potentially reducing the board area and number of layer requirements. This concept, again, relies on the existence of a hardware-software-FPGA development environment that is connected at the platform level, as this is required to support intelligent and automated pin-swapping between the hardware-FPGA domains.

This unified design approach also opens up the possibility of implementing global software systems that raise the abstraction of the design process – such as schematic or graphically based embedded design

Figure 2 | Flexible SoC systems, including external "hard" components, can be plugged together using FPGA-based Wishbone bus architecture cores that act as versatile interfacing layers.

capture that is synchronized to both the hardware and software domains.

The natural extension of this design abstraction is to implement high-level embedded layers that effectively disconnect the soft elements of a design from the hardware on which it resides (Figure 2). These inserted layers "normalize" the interfaces between processors and hardware such as memory and peripherals, removing the need to deal with the low-level hardware complexity of I/O configurations and bus systems. Reconfiguring an FPGA design becomes a simpler, lower risk process, whether it's rebirthing legacy designs, configuring different production modes, reusing established IP, or performing postproduction updates.

In practice, processors and peripherals can be supported by library-based FPGA cores based on the Wishbone bus architecture. The core abstracts a processor interface by effectively "wrapping" around the device, making it architecturally equivalent to other processors. It therefore allows a processor to be opportunistically changed without affecting the connected peripherals or forcing major redesign. Along with FPGA-based "soft"

devices, the concept can be extended to include hybrid hard-core processors, external processors, and off-chip discrete peripherals and memory devices.

#### **Next-generation FPGA design**

The high-level unified embedded design approach outlined is made possible by capitalizing on the reprogrammable capability of the FPGA host. Any imposed layers and interfaces are automatically included in the FPGA's fabric, along with the functional design itself, enabling the hardware design to be dynamically explored without fatally disrupting the other parts of the design.

**Rob Evans** is a technical editor at Altium Limited. He has more than 20 years of experience in the electronics design and publishing industry, and studied

Electronic Engineering at RMIT in Melbourne, Australia. Rob can be contacted at rob.evans@altium.com.

> **Altium Limited** 1-800-544-4186 www.altium.com

Considering the environmentally intense environments faced by modern military electronics, the ability to meet the widest range of ruggedization and operating temperature requirements is an absolute must. And, when traditional Direct Forced Air (DFA) and conduction-cooling techniques are insufficient, designers are turning to more advanced approaches to save the day: Airflow Through (AFT) cooling, spray cooling, and Liquid Flow Through (LFT) cooling.

Embedded COTS boards for deployed aerospace and defense applications have to be able to meet the widest range of operating temperature and ruggedization requirements. From air-cooled cards in relatively spacious racks aboard naval platforms, to conduction-cooled cards located in crowded corners of fighter jets, today's COTS boards need to perform on the tarmac of the desert at noon as well as in the cold environs of high-altitude flight.

With the increasing popularity of highly integrated small form factor 3U cards to deploy compute power in space-, weight-, and power-constrained platforms, embedded system designers are faced with an array of cooling approaches to address heat dissipation in rugged deployed COTS systems. When traditional Direct Forced Air (DFA) and conduction-cooling techniques aren't sufficient to handle cooling requirements (that is, -40 °C to +71 °C ambient), system designers must turn to advanced approaches such as Airflow Through (AFT) cooling, spray cooling, and Liquid Flow Through (LFT) cooling. Each of these cooling approaches has its particular advantages as well as design considerations to weigh before choosing which is the right one to adopt.

#### Airflow Through cooling

One recent entry to the realm of higherpower cooling approaches for military COTS circuit cards is AFT cooling. Though relatively new to the military COTS cooling arsenal, AFT has been used by systems integrators for many years, most often in the form of an aircooled duct featuring some metal finning. These ducts are called "compact core heat exchangers." In these applications, AFT is typically implemented by bonding two single-sided PWBs to either side of the heat exchanger. Unfortunately, that is not really viable for COTS because virtually all available military COTS cards are double-sided, with components resident on each side.

When applied to COTS cards, AFT can be implemented by placing the heat exchanger on the top of the primary side of the circuit card (see Figure 1). Mezzanine cards can then be placed on top of the heat exchanger. While similar to DFA cooling in that air is blown over the electronics to cool the card, there is no direct contact of the air with the electronics. This eliminates the risk of exposure to contaminants in the air that must be considered with DFA. For AFT to work properly, air seals must be provided at

the heat exchanger inlet and outlet of AFT cards. These are typically applied on the chassis side and need to be able to withstand hundreds of insertions and extractions. Additional features of AFT cards are retainers and injectors/ejectors, all of which are being standardized in VITA 48.5, the AFT standard, which is currently in draft form.

With AFT cards using similar airflow rates to DFA, it is possible to cool boards rated at up to 200 W. While AFT should be considered more of a midpower cooling approach, it is superior to forced air and conduction cooling. The limits of AFT are related to the use of air for cooling, as they are with DFA as well. An asymptotic curve develops as

Figure 1 | 6U AFT module with air heat exchanger mounted on primary side of military COTS circuit card. This module can cool >200 W with +55 °C inlet air.

Hardware: Designing in *cool* reprogrammability

the amount of air flowing over the heat exchanger increases. Compared to DFA, the decline in effectiveness is not as sharp because AFT employs an enclosed duct that can be made quite smooth. This duct and the smooth surface result in less flow bypass and lower pressure drops compared to those created by the natural ducts formed between two DFA cards, in which the components on the card surfaces present a rough route for the air to travel over.

#### Spray cooling

A chassis-level implementation of spray cooling uses a mist of coolant directed at the circuit cards. When the coolant hits the circuit card hot spots, it vaporizes and then condenses within the chassis. Alternatively, the coolant can be sent to a remote heat exchanger where it is condensed further and pumped back into the chassis in a closed-loop system. Because spray cooling is able to cool very high power densities (such as processor die) to relatively low temperatures (such as -70 °C to +75 °C), it can enable the use of true commercial-grade circuit cards (0 to +70 °C) in rugged deployed applications. In comparison, rugged COTS cards are typically designed to -40 °C to +71 °C or higher temperature ranges.

Spray cooling can also be used to mitigate cold startup issues. At the low end of the temperature range, the coolant can be heated to warm the electronics before they are turned on. One drawback to this approach, though, is that the commercial circuit cards need to be so-called "spray" ready. For example, any air cooled heat sinks on the cards need to be removed because the spray needs to be directed at the component or the die. Also, the circuit card must use materials, the thermal interface materials in particular, that are compatible with the type of coolant in the spray-cooled system.

Other drawbacks of spray cooling are the additional weight and volume that the apparatus adds to the chassis (roughly 50 percent) as well as the increased cost and complexity of the system. In addition, spray-cooling systems, unlike LFT cooling systems (to be discussed in the next section), are dependent on the physical orientation of the hardware because of unfavorable gravity force (and other body forces like acceleration) effects on the condensed liquid.

#### Liquid Flow Through cooling

LFT is another relatively recent entrant into the ranks of military COTS cooling options, though it has been used for many years (if not decades) by system integrators in costly custom configurations. While similar to AFT, instead of an air-cooled heat exchanger LFT employs a liquid cooled heat exchanger, which in military COTS systems is typically placed on the primary side of the circuit card. The design of the heat exchanger will vary greatly depending on the heat density and heat distribution of the card to be cooled. As the liquid flows through the cores, it picks up the heat and then flows out at an end point. Liquids have much higher heat capacities than air [that is, 1-10 J/(cm $^{3}$ °K) vs. ~10 $^{-3}$  J/(cm $^{3}$ °K)], allowing cooling of higher powers in narrower pitches. For example, LFT can efficiently cool boards with a 0.85" pitch for which AFT would need at least a 1.5" pitch. One design consideration for LFT, however, is that the liquid coolant requires an air heat exchanger at some point, which adds weight and volume to the system.

Two-level maintenance LFT systems have the additional requirement of Quick Disconnect (QD) liquid connectors that close the liquid loop between the chassis and the module. These QDs and other features of LFT for COTS systems are currently being standardized within VITA:

- VITA 48.3: Defines an approach where the liquid manifold is located in the chassis below the backplane

- VITA 48.4: Enables the liquid manifold to be placed above the backplane, which eases use of a standard ATR height chassis

- VITA 48.6: For use with LFT modules larger than 6U

Parker Hannifin and Curtiss-Wright Controls designed, manufactured, and tested an LFT module with some specific attributes in the cover that was able to cool more than 650 W (see Figure 2). This impressive result was achieved at +55 °C with a liquid coolant called PAO, a synthetic oil which has a relatively poor heat capacity. This project highlighted a particular benefit of LFT: the ability to use spreadsheet calculations to accurately predict thermal performance. This is not the case with air-cooling approaches,

While the need for higher-performance processing in smaller environments continues its inexorable rise, the military COTS industry is meeting the challenge with advanced cooling methods to stay ahead of the heat curve.

which typically require the use of Computational Fluid Dynamics (CFD) tools for accurate thermal predictions.

Figure 2 | 6U LFT module with liquid heat exchanger mounted on primary side of military COTS circuit card. This module can cool >650 W with +55 °C inlet PAO coolant.

The design considerations for LFT include the risk of leakage from the QDs, as well as the resultant increase in weight, volume, and system complexity. LFT does, however, eliminate the orientation dependence of spray-cooling systems because it uses pumped, single-phase cooling.

#### Staying ahead of the heat curve

While the need for higher-performance processing in smaller environments continues its inexorable rise, the military COTS industry is meeting the challenge with advanced cooling methods to stay ahead of the heat curve. Going beyond air and conduction cooling requires more complexity and greater system challenges, such utilizing relatively new cooling methods of AFT, spray, and LFT cooling. The open standards community is tackling these challenges to ensure that today's best computing technology is available to the warfighter in the most demanding and harshest environments.

**Ivan Straznicky** is a principal mechanical engineer for Curtiss-Wright Controls Embedded Computing, where his responsibilities include advanced thermal and packaging technologies. Ivan is currently the vice chair of the VITA Standards Organization and a key contributor to the following standards/ specifications: ANSI/VITA 46, ANSI/VITA 47, VITA 48, and VITA 42. He has a degree in Mechanical Engineering

from McGill University in Montreal, Canada. He can be contacted at ivan.straznicky@curtisswright.com.

> **Curtiss-Wright Controls Embedded Computing** 613-599-9199 www.cwcembedded.com

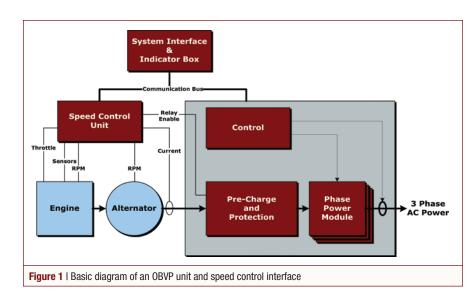

enables more effective power supply to current and emerging battlefield electronic systems by providing improved physical characteristics, in addition to more effective power disbursement than traditional "Tactical Quiet Generators," thanks to new OBVP inverter technology.

The deployed U.S. soldier is given every technological advantage possible on the battlefield. U.S. warfighters have become more than rifle carriers, now utilizing a vast array of military systems active in any number of methods: From on-site radar and threat evaluation systems to UAV patrols to fighter-mounted thermographic and spectral imaging, these systems have provided the ability to not only outgun but completely control an occupied space.

A push is underway to make the U.S. military more agile, mobile, and lethal. To do so requires new weapons systems and next-generation computational systems. Many of these services and applications fall under the Army Brigade Combat Team (BCT) modernization strategy (formerly Future Combat Systems). Some of these most advantageous next-generation military applications involve high-density computational systems that can perform functions such as RF/spectrum scanning and analysis, dispersion analysis, locational detection, cryptanalysis, horizon bogey detection and threat prediction (as opposed to simple evaluation), and probability analysis directly on the battlefield, providing real-time information to on- and off-battlefield commanders. These applications are invaluable to the warfighter in the modern theater and are critical to maintaining situational awareness for the battlefield commander and dominance of active war space.

When talking of these next-generation battlefield systems, an often overlooked but critical question must be addressed: How does one power them? It is not possible to simply plug into an outlet in the middle of a desert. The move to these sophisticated battlefield applications will raise the demand for power exponentially.

Consequently, the rise in demand of power for these advanced deployed systems means an increase in the output of power required from generator systems. With traditional skid-mounted or trailer-towed fuel power technologies, the end result is reduced to nothing more than larger, heavier, and more fuel-hungry generators. This is in direct opposition to the nearly decade-old emphasis to create a faster, lighter, and more agile deployed force. However, new On Board Vehicle Power (OBVP) systems are providing a viable remedy with an improved physical design and new inverter technology for more effective power disbursement.

#### Traditionally deployed power systems: **Designs no longer sufficient**

As mentioned, traditionally, theaterdeployed systems are powered by trailertowed or skid-mounted generators. Hitched directly to an HMMWV, these towed generators require ample diesel (fuel) to operate, reduce troop mobility and response times, and, when in operation at a site, are frequently giveaways to

the adversary as to the intentions and location of the camped troops. These "Tactical Quiet Generators" have been in use since the late 1980s and require the carrying of additional fuel to generate power. Skidmounted units also drastically reduce the cargo capacity of the HMMWV, as they are typically carried in the rear cargo area of the vehicle.

In the past, commanders were dealing with defined combat lines and specific operational theaters and occupation directives. In the modern theater this is no longer the case, and power generators and techniques of the past cannot power the military and its systems of the future. While technology has improved, certain characteristics such as noise, lack of mobility, serviceability constraints, the need for extra vehicles to carry fuel and generators, and other logistical issues that are inherent to the design and use of these Tactical Quiet Generators have created battlefield nightmares for the operators (not to mention increased costs and the swelling of budgets for commanders to accommodate these logistical shortcomings). And all of these issues are in direct opposition to the current military push of "lighter, faster, stronger, smarter." They must be overcome to maintain Armed Forces dominance of an active theater.